- 您现在的位置:买卖IC网 > Sheet目录342 > MCZ33927EK (Freescale Semiconductor)IC FET PRE-DRIVER 3PH 54-SOIC

�� �

�

FUNCTIONAL� DEVICE� OPERATION�

�LOGIC� COMMANDS� AND� REGISTERS�

�STATUS� REGISTERS�

�After� any� SPI� command,� the� status� of� the� IC� is� reported� in�

�the� return� value� from� the� SPI� port.� There� are� four� variants� of�

�the� NULL� command� used� to� read� various� status� in� the� IC.�

�Other� commands� return� a� general� status� word� in� the� Status�

�Register� 0.�

�There� are� four� Status� Registers� in� the� IC.� Status�

�Register� 0� is� most� commonly� used� for� general� status.�

�Registers� one� through� three� are� used� to� read� or� confirm�

�internal� IC� settings.�

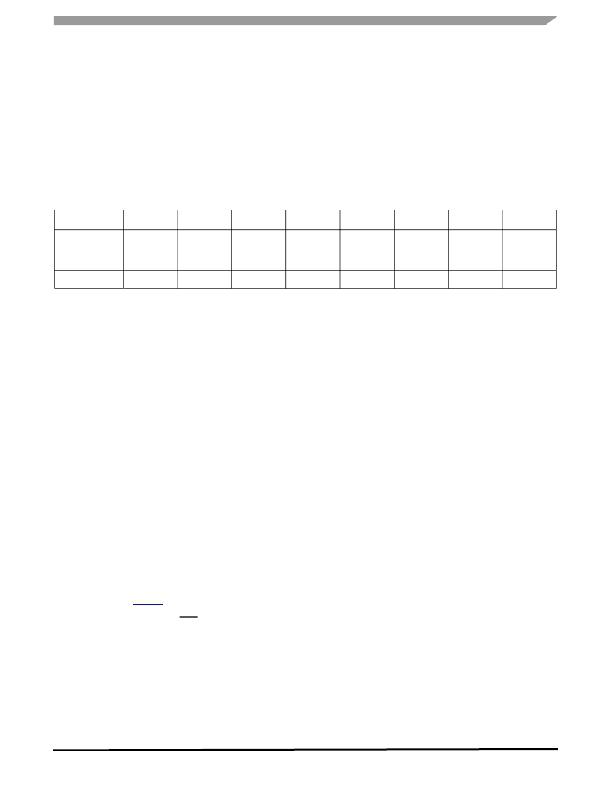

�Status� Register� 0� (Status� Latch� Bits)�

�This� register� is� read� by� sending� the� NULL0� command� (000x� xx00).� It� is� also� returned� after� any� other� command.� This� command�

�returns� the� following� data:�

�Table� 14.� Status� Register� 0�

�SPI� Data� Bits�

�Results�

�Register� 0�

�Read�

�Reset�

�7�

�RESET�

�Event�

�1�

�6�

�Write�

�Error�

�0�

�5�

�Framing�

�Error�

�0�

�4�

�Phase�

�Error�

�0�

�3�

�Overcurrent�

�0�

�2�

�Low�

�VLS�

�0�

�1�

�DESAT�

�Detected� on�

�any� Channel�

�0�

�0�

�TLIM�

�Detected� on�

�any� Channel�

�0�

�All� status� bits� are� latched.� The� latches� are� cleared� only� by� sending� a� CLINT0� or� CLINT1� command� with� the� appropriate� bits�

�set.� If� the� status� is� still� present,� that� bit� will� not� clear.� CLINT0� and� CLINT1� have� the� same� format� as� MASK0� and� MASK1�

�respectively.�

�?� Bit� 0� –is� a� flag� for� Overtemperature� on� any� channel.� This� bit� is� the� OR� of� the� latched� three� internal� TLIM� detectors.This�

�flag� can� generate� an� interrupt� if� the� appropriate� mask� bit� is� set.�

�?� Bit� 1� –is� a� flag� for� Desaturation� Detection� on� any� channel.� This� bit� is� the� OR� of� the� latched� three� internal� high-side�

�desaturation� detectors� and� phase� error� logic.� Faults� are� also� detected� on� the� low-side� as� phase� errors.� A� phase� error� is�

�generated� if� the� output� signal� (at� Px_HS_S)� does� not� properly� reflect� the� drive� conditions.� The� phase� error� is� the� triple� OR�

�of� phase� errors� from� each� phase.� Each� phase� error� is� the� OR� of� the� HS� and� LS� phase� errors.� An� HS� phase� error� (which�

�will� also� trigger� the� desaturation� detector)� occurs� when� the� HS� FET� is� commanded� on,� and� the� Px_HS_S� is� still� low� in� the�

�deadtime� duration� after� it� is� driven� ON.� Similarly,� a� LS� phase� error� occurs� when� the� LS� FET� is� commanded� on,� and� the�

�Px_HS_S� is� still� high� in� the� deadtime� duration� after� the� FET� is� driven� ON.� This� flag� can� generate� an� interrupt� if� the�

�appropriate� mask� bit� is� set.�

�?� Bit� 2� –� is� a� flag� for� Low� Supply� Voltage� .� This� bit� is� latched,� thus� a� prior� low� voltage� event� is� returned� once� before� being�

�cleared� on� read.� This� flag� can� generate� an� interrupt� if� the� appropriate� mask� bit� is� set.�

�?� Bit� 3� –is� a� flag� for� the� output� of� the� Overcurrent� Comparator� .� This� flag� can� generate� an� interrupt� if� the� appropriate� mask�

�bit� is� set.�

�?� Bit� 4� –is� a� flag� for� a� Phase� Error� .� If� any� Phase� comparator� output� is� not� at� the� expected� value� when� just� one� of� the�

�individual� high-� or� low-side� outputs� is� enabled,� the� fault� flag� is� set.� This� signal� is� the� XOR� of� the� phase� comparator� output�

�with� the� output� driver� state,� and� blanked� for� the� duration� of� the� desaturation� blanking� interval.� This� flag� can� generate� an�

�interrupt� if� the� appropriate� mask� bit� is� set.�

�?� Bit� 5� –is� a� flag� for� a� Framing� Error� .� A� framing� error� is� a� SPI� message� not� a� multiple� of� eight� bits� (a� 0-length� message� is�

�also� a� framing� error),� or� SI,� or� SCLK� toggling� detected� while� measuring� the� Deadtime� calibration� pulse.� This� would� typically�

�be� a� transient� or� permanent� hardware� error,� perhaps� due� to� noise� on� the� SPI� lines.� This� flag� can� generate� an� interrupt� if�

�the� appropriate� mask� bit� is� set.�

�?� Bit� 6� –indicates� a� Write� Error� After� the� Lock� bit� is� set.� A� write� error� is� any� attempted� write� to� the� MASKn,� Mode,� or� a�

�Deadtime� command� after� the� Mode� Lock� bit� is� set.� A� write� error� is� any� attempt� to� write� any� other� command� than� the� one�

�defined� in� the� Table 7� .� This� would� typically� be� a� software� error.� This� flag� can� generate� an� interrupt� if� the� appropriate� mask�

�bit� is� set.�

�?� Bit� 7� –is� set� upon� exiting� RST� .� It� can� be� used� to� test� the� interrupt� mechanism� or� to� flag� for� a� condition� where� the� IC� gets�

�reset� without� the� host� being� otherwise� aware.� This� flag� can� generate� an� interrupt� if� the� appropriate� mask� bit� is� set.�

�33927�

�Analog� Integrated� Circuit� Device� Data�

�Freescale� Semiconductor�

�33�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MCZ33937EKR2

IC PRE-DRIVER 3PHASE 54-SOIC

MDN2BL3GRAS

MOTOR BRUSHED DC 2V 2753RPM

MDN3BL3CSAS

MOTOR BRUSHED DC 2V 1458RPM

MIC2287-34YML TR

IC LED DRIVER WHITE BCKLGT 8-MLF

MIC2289C-34YD6 TR

IC LED DRIVR WHITE BCKLGT TSOT-6

MIC2291YD5 TR

IC LED DRIVER PHOTO FLASH TSOT-5

MIC2293-15YML TR

IC LED DRIVER WHITE BCKLGT 8-MLF

MIC2293C-34YML TR

IC LED DRIVER WHITE BCKLGT 8-MLF

相关代理商/技术参数

MCZ33927EK/R2

制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Three-Phase Field Effect Transistor Pre-Driver

MCZ33927EKR2

功能描述:功率驱动器IC THREE PHASE PRE- DRIVER RoHS:否 制造商:Micrel 产品:MOSFET Gate Drivers 类型:Low Cost High or Low Side MOSFET Driver 上升时间: 下降时间: 电源电压-最大:30 V 电源电压-最小:2.75 V 电源电流: 最大功率耗散: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8 封装:Tube

MCZ33927R2

制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Three-Phase Field Effect Transistor Pre-Driver

MCZ33937AEK

功能描述:马达/运动/点火控制器和驱动器 3 Phase Pre-Driver RoHS:否 制造商:STMicroelectronics 产品:Stepper Motor Controllers / Drivers 类型:2 Phase Stepper Motor Driver 工作电源电压:8 V to 45 V 电源电流:0.5 mA 工作温度:- 25 C to + 125 C 安装风格:SMD/SMT 封装 / 箱体:HTSSOP-28 封装:Tube

MCZ33937AEK/R2

制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Three Phase Field Effect Transistor Pre-driver

MCZ33937AEKR2

功能描述:马达/运动/点火控制器和驱动器 3 Phase Pre-Driver RoHS:否 制造商:STMicroelectronics 产品:Stepper Motor Controllers / Drivers 类型:2 Phase Stepper Motor Driver 工作电源电压:8 V to 45 V 电源电流:0.5 mA 工作温度:- 25 C to + 125 C 安装风格:SMD/SMT 封装 / 箱体:HTSSOP-28 封装:Tube

MCZ33937EK

功能描述:功率驱动器IC THREE PHASE PRE DRIVER RoHS:否 制造商:Micrel 产品:MOSFET Gate Drivers 类型:Low Cost High or Low Side MOSFET Driver 上升时间: 下降时间: 电源电压-最大:30 V 电源电压-最小:2.75 V 电源电流: 最大功率耗散: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8 封装:Tube

MCZ33937EK/R2

制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Three Phase Field Effect Transistor Pre-driver